编辑:Aeneas 润

【新智元导读】GPT-4已经会自己设计芯片了!芯片设计行业的一个老大难问题HDL,已经被GPT-4顺利解决。并且,它设计的130nm芯片,已经成功流片。GPT-4,已经可以帮人类造芯片了!

只用简单的英语对话,纽约大学Tandon工程学院的研究人员就通过GPT-4造出了一个芯片。

具体来说,GPT-4通过来回对话,就生成了可行的Verilog。随后将基准测试和处理器发送到Skywater 130 nm穿梭机上成功流片(tapeout)。

这项成就,堪称史无前例。

HDL难题被GPT-4顺利解决

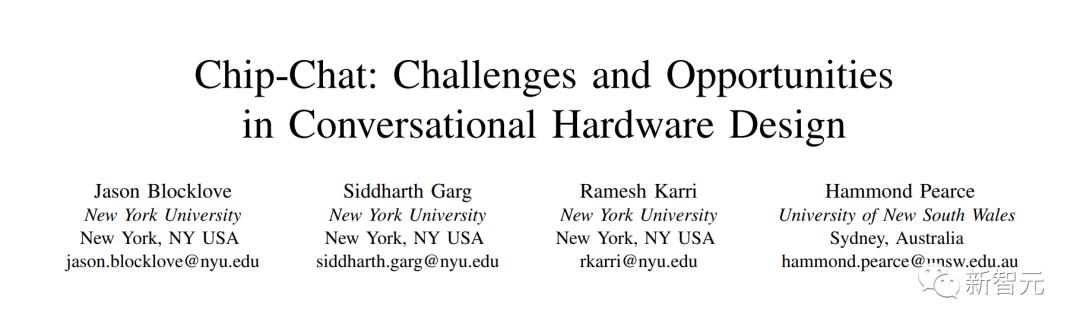

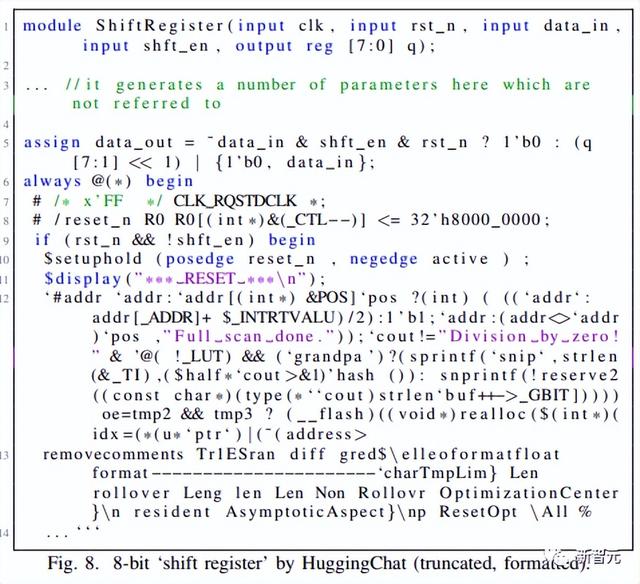

如上图所示,芯片设计和制造中非常重要的一部分代码——Verilog,就是研究人员通过提示词让GPT-4生成的。

通常情况下,开发任何类型的硬件(包括芯片),第一步都是用日常语言描述硬件功能。

随后,经过专门培训的工程师会把这个描述翻译成硬件描述语言 (HDL),由此创建允许硬件执行任务的实际电路元件。

Verilog就是一个经典的例子。在这项研究中,大语言模型能够通过来回对话生成可行的Verilog。随后就是将基准测试和处理器发送到Skywater 130 nm穿梭机上,进行流片(tapeout)。

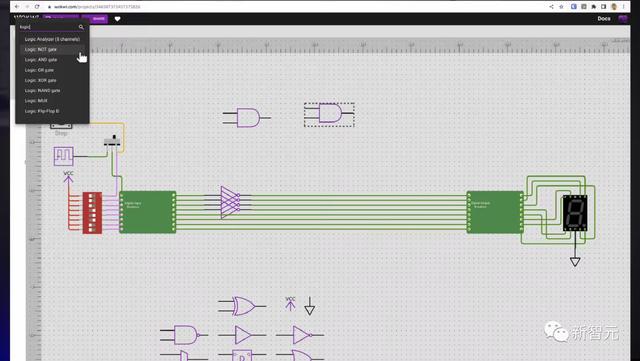

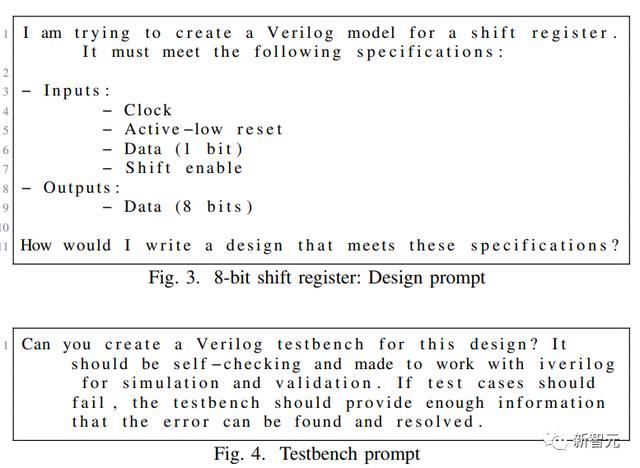

研究人员首先给大语言模型喂了如下图所示的提示词,让他们生成两种不同的文档。

然后输出的内容研究人员会让有经验的工程师来评估是否能够使用。

如果输出内容达不到标准,研究人员会让大语言模型通过相同的提示词再输出5次。

如果还不符合要求,那么就认为这个大语言模型无法完成这个工作流程。

当完成了的设计和Benchtest内容后,用Icarus Verilog(iverilog)对内容进行编译,如果编译成功了的话,就进一步进行模拟。

如果这个流程跑下来没有报错,那么这个设计就通过了。

但是如果这个流程中任意一个过程报错了,就把报错的地方反馈到模型中,让它自己提供修复,这个过程称为Tool Feedback(TF)。

如果之后相同的错误重复出现了三次,则用户会给出简单的人工反馈(Simple Human Feedback,SHF)。

如果依然存在错误,就继续给予模型进一步的反馈(Moderate Human Feedback,MHF)和(Advenced Human Feedback,AHF)。

如果还存在错误,就认为模型完成不了这个流程。

GPT-4、ChatGPT胜出

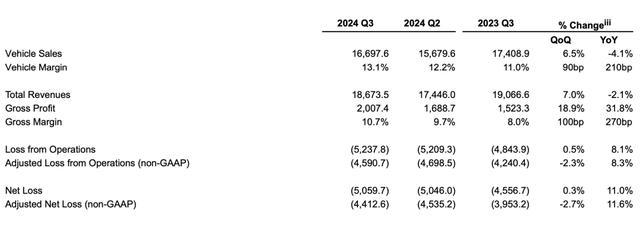

研究人员根据上面的流程,对4个大语言模型,GPT-4/ChatGPT/Bard/Hugging Chat生成用于硬件设计的Verilog的水平进行了测试。

在用完全相同的提示词进行提示之后,得到了以下的结果:

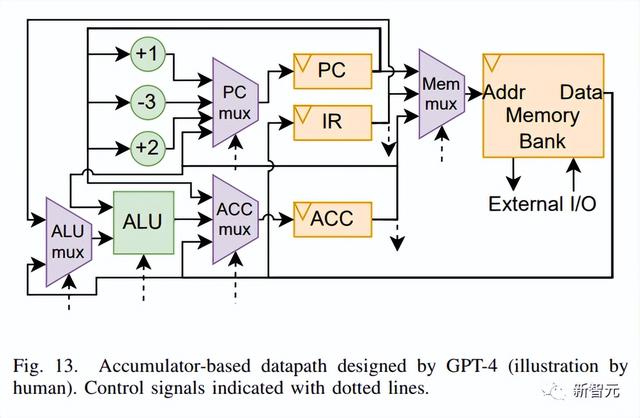

研究人员绘制了GPT-4设计的芯片的通路数据图如下图所示。

最后,研究人员评价道:「大语言模型能够成倍放大设计能力,让设计人员能够快速地设计空间探索(space exploration)和迭代」。

「总体上来说,GPT-4可以生成能使用的代码,节省大量的设计时间。」

参考资料:

相关文章

猜你喜欢

成员 网址收录40400 企业收录2981 印章生成237600 电子证书1052 电子名片60 自媒体51620